Depuis les années 60, la puissance de calcul suit une progression selon la « loi de Moore » qui dit que la quantité des puces électroniques dans un circuit intégré dense est doublée tous les deux ans.

Cependant, ces dernières années, les contraintes physiques au niveau des atomes commencent à avoir un réel impact sur la vitesse à laquelle on peut faire progresser la densité des puces électroniques. Les entreprises qui font les designs commencent à regarder du côté des circuits spécifiques pour les différentes tâches, dont l’apprentissage automatique.

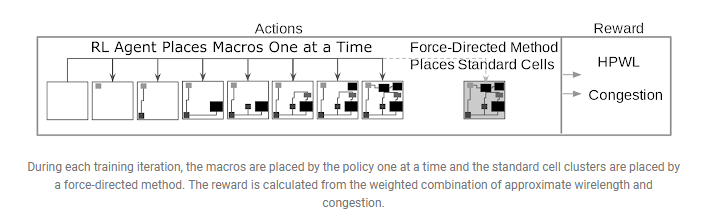

C’est dans ce contexte que des chercheurs au sein des équipes du projet de recherche Google Brain se sont interrogées sur la possibilité pour des algorithmes d’apprentissage par renforcement d’agencer correctement des composants dans la puce. Le résultat : ils ont obtenu des agents capables de créer des designs aussi performants que ceux réalisés par des experts, et cela en moins de 6 heures. L’une des applications les plus récentes réside dans la conception des dernières versions des TPU (Tensor Processing Unit).

Découvrez l’article de référence :

A graph placement methodology for fast chip design

Auteurs : Azalia Mirhoseini, Anna Goldie et al.

Source : https://www.nature.com/articles/s41586-021-03544-w.pdf

Schéma et iconographie : AI Google Blog, Freepik

Parution le : 09/06/2021

Voir aussi :

- Quand l’IA arrive à contrôler le plasma dans les réacteurs tokamaks

- Les transformers passent du langage naturel au développement de code

Envie de rester informé(e) ?

Abonnez-vous à la Newsletter Scal[ia]

Articles connexes